wand and wor data types in Verilog |

Any verilog module has input, output and potentially some innner net connections. In some cases, the inner connections are could be driven by more than one gate or more than one driver.

Wand and wor are net data types that specify how this common net will be connected. If we simply specify wire in place of wand or wor, they simple connect the net driven by two gates together.

If a net is declared as wand data type then, you can assume the output to be zero whenever any of the two or more gates or drivers are 0. In other words, the two or more outputs are fed into an AND gate and final output is ANDed result of these outputs.If the wire is declared as wor, the output is forced to 0 if any of the drivers is 1. In other words the two or more outputs from the gates are ORed.

The wire and wand net declaration forces sythesizer to insert AND or OR gate if required. Notice that, if he design does not result in the net being driven by more than one gate or driver, the AND or OR gate may not be required. Consider the following verilog module

module comparatorwithwor( input x, input y, output z ); wor p ; assign p = x&y; assign p = ~x & ~y ; assign z = p ; endmodule |

The net p is driven by the outputs of two AND gates as given by the assign statements

assign p = x&y; assign p = ~x & ~y ; |

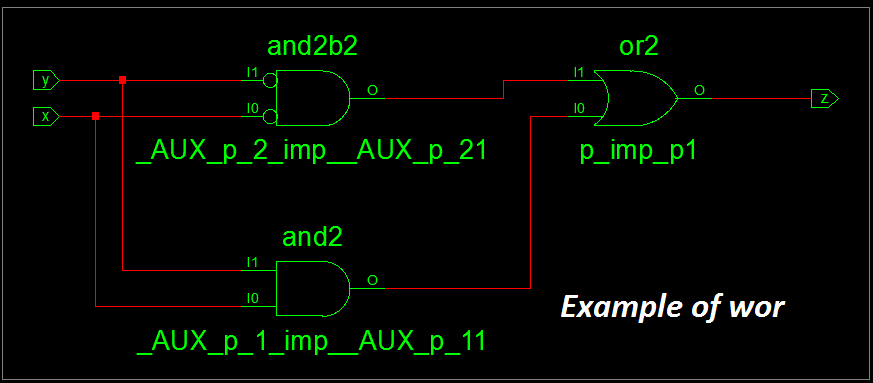

However, since p is assigned as wor, the synthesizer inserts an OR gate. The input to the OR gate is the driver of the two AND gates. This is the synthesized output as shown by Xilix ISE.

Notice that we we declare p as wire in place of wor, as in

module comparator( input x, input y, output z ); wire p ; assign p = x&y; assign p = ~x & ~y ; assign z = p ; endmodule |

We get the following error as reported by Xilinx.

Multi-source in Unit

If we do not want to use wor and wish to implemment this design just using wire, we can do it as follows.

module comparator( input x, input y, output z ); wire p,q ; assign p = x&y; assign q = ~x & ~y ; assign z = p |q ; endmodule |

Here is the youtube from Prof. Sengupata where he talks about wand and wor.

Personally we believe that wand and wor should be avoided, unless you know exactly what it is doing. It still may have academic use and hence the material.