Interview Questions in Verilog

11. What is duty cycle?

Duty Cycle is the fraction of time the signal is high or low. It represents on time of a signal. It can be represented by D=T/P where Dis the duty cycle,T is the time signal is active and P is the total time period of signal.

12. What is $random?

$random is used to generate random numbers to identify hidden bugs in program. It returns 32 bit number. It returns a new random number each time the function is called. It can also contain

$random;

$random();

13. Write a Verilog code for synchronous and asynchronous reset? Example:- a.

always @(poseedge clk) //synchronous reset is clock dependent

begin

If (reset)

else

end

b. always @(posedge clock or posedge reset) //Asynchronous reset is clock independent

begin

if(reset)

end

14. What is the difference between blocking and nonblocking assignment?

Table: Difference between Blocking and non blocking assignment statements

| Wire | Reg |

| The whole statement is done before Control passes to next statement |

It evaluates all the RHS at current time unit and assign to LHS at the end of the time unit. |

| It uses = operator | It uses <= operator |

15. What is the difference between task and function? Table: difference between task and function

| Function | Task |

| Function can invoke another function but not task | Task can invoke another task or function |

| Function doesn�t contain timing constraints | Task can contain timing constraints<= operator |

| Function must have at least one input argument | Task can contain input, output, inout as argument |

| Function always return single value | Task does not return value but pass multiple values through output or inout ports. |

16. What are different types of delay control?

a) Regular delay control

b) Intra assignment delay control

c) Zero delay control

Example:- //Intra assignment delay control reg a,b,c; Initial begin a=0,b=0; c= #5 a+b; /* Takes value of a and b at time 0 evaluates a+b and then waits 5 time units to assign value to c */ end //Regular delay control a=0,b=0; Initial begin temp=a+b; #5 c=temp /*Evaluates a+b at current time unit and stores it in temprory variable and then assign it to c at 5 time units */ end //Zero delay control initial begin a=0; b=0; end Intial begin #0 a=1; //Zero delay control #0 b=1; end /* In above code a=0,b=0,a=1.b=1 are to be excuted at simulation time zero but a=1 and b=1 are excuted after a=0,b=0 as zero delay control is applied to these statements. */ |

17. What do you mean parallel block?

In parallel block all statements are executed concurrently(ie not sequential) They are specified by keyword fork and join. Timing constraints can be provided in parallel block. Example:-

module parallel; reg a,b,c; initial begin $monitor ("%g,a=%b,b=%b,c=%b",$time,a,b,c); fork #1 a=0; #5 b=1; #10 c=0; join #1 $display ("%g EXIT",$time); end endmodule |

In the above code a gets 0 after 1 time unit,b after 5 time unit,c after 10 time units ,EXIT after 11 time units

18. What is $time in Verilog?

$time function is invoked to get the current simulation time.A time variable is a special register data type to store simulation time.$time returns 64bit integer value. Example:-

time curr_time; initial curr_time = $time; |

19. What is defparam?

Parameter values can be overridden by use of defparam keyword at module instance.It can also change the parameter values at different time interval within the module. Example:-

module hello; parameter p1 = 0; initial $display ("hello p1 = %d",p1); endmodule module Top; defparam c1.p1 = 2,c2.p1 = 3; //Parameter values are overridden in module Top hello c1();//module instance of hello hello c2(); endmodule |

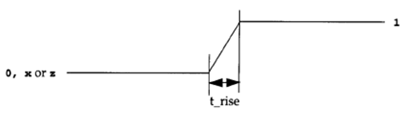

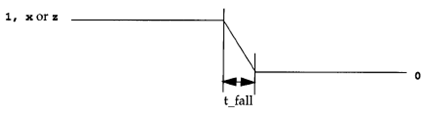

20. What is rise,fall and turnoff delays?

a. Rise delay indicates gate output transition from any value to 1

b. Fall delay indicates gate output transition from any value to 0

c. Turnoff delay indicates gate output transition from any value to z

Each delay mentioned above has min\typ\max values.These values are used because of the variation in IC fabrication process.

Each delay mentioned above has min\typ\max values.These values are used because of the variation in IC fabrication process.

Syntax:-

#(rise fall turnoff)