Interview Questions in Verilog

1. What is the difference between wire and reg?

Table: Difference between Wire and reg

| Wire | Reg |

| Assumes Value | Holds Value |

| wire needs drivers to get output values | reg does not need driver |

| wire elements can only be used to model combinational logic |

reg can be used for combinational as well as sequential logic |

| wire can be used as the left hand side of an assign statement |

reg cannot be used on the left-hand side of an assign statement |

2. What do we mean by continuous assignment ?

Continuous assignment is used to drive values to net. Left hand side can be scalar or vector net or concatenation of both while right hand side can be scalar or vector net or register or concatenation of both. Read more here .

3. What do we mean by full case and parallel case?

A full case is a case statement in which all possible all possible case expression can be matched with case items or case default. If it is possible to find binary expression that doesn't case item the case statement is not full. A parallel case statement is a case statement in which it is possible to match a case expression with one and only one case item if it is possible to find a case expression that would match more than one case item the matching case is called overlapping or non parallel.

4. What is the difference between $monitor and $display.

$monitor and $display both system functions and are both used to see the testbench results.

Table: Difference between $monitor and $display

| $monitor | $display |

| Monitors change in the value of signal. Signal can be variable, strings or expression. |

Displays the value of signal. |

| Can be invoked once | Can be invoked more than once. |

5. What is $strobe?

It is a synchronization mechanism in which data is displayed only after all other statements are executed unlike $display in which execution order could be nondeterministic.

6. What is meant by inferring latches and how to avoid it?

Inferring latch means to reproduce last value when unknown branch is specified. For example, to avoid latches make sure that all cases are mentioned in case statements if not case default is mentioned. In the same way latch is inferred in IF statement if ELSE IF is not specified.

always @(s1 or s0 or i0 or i1 or i2 or i3)

case ({s1,s0})

2'b00 : out = i0;

2'b01 : out = i1;

2'b10 : out = i2;

endcase

In above example code of 4to1 multiplexer all combinations are not compared and default is also not used so latch is inferred to reproduce previous value.

7. What is the difference between == and === operator?

Output of == can be 0,1,X while output of === is always 0 or1.

== doesn't compare X and if at least one bit is X output will be X.=== compare X bits and output is always 0 or 1 accordingly.

8. What is the difference between $setup and $hold?

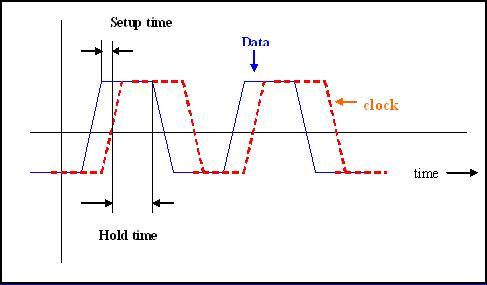

$setup and $hold is used to monitor setup and hold time constraints for sequential logic. Setup time is the minimum time the data must arrive before active edge of clock signal and hold time is the minimum time the data cannot change after active edge of clock signal. They are specified under specify block.

Draw following diagram to explain.

9. What is casex and casez statement?

These are the types of case statement in which casex represent x and z as don't care while casez represent z as don't care. Don't cares are not allowed in case statement so casex and casez are used.

10. What is repeat loop in Verilog?

Repeat loop is used to execute loop fixed number of times. It is not used to loop expression like we see in while loop statement. It contains constant, variable or signal . For example repeat(8)